10나노 '벽' 누가 먼저 넘나…삼성·인텔·TSMC 삼국지

기사입력 2014-11-30 10:07

|

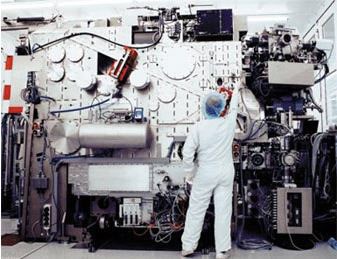

| ASML의 노광기. /조선일보DB |

대만의 반도체회사 TSMC가 차세대 기술인 10나노미터(㎚) 공정을 적용한 반도체 생산 준비 작업에 착수했다. 세계적인 반도체 장비업체인 네덜란드ASML은 이달 24일 영국 런던에서 열린 기업설명회(IR)에서 대만 TSMC에 극자외선(EUV) 노광장비 2대를 공급하기로 했다고 밝혔다. 이 장비는 10나노 공정에서 반도체 실리콘 원판(웨이퍼)에 회로의 밑그림을 그리는 핵심적인 장비에 속한다.

노광기 한대 가격은 이건희 삼성전자(005930)회장의 새 전용기인 ‘B737-7EG’(약 855억)의 가격보다 많은 1000억원을 웃돈다. 전 세계에서 이 장비를 만든느 업체는 ASML이 유일하다.

TSMC가 10나노 공정에 가장 먼저 착수하면서 삼성전자와 인텔 등 경쟁사들의 발걸음도 바빠지게 됐다.

◆ ‘10나노 공정’ 스타트 끊은 대만 TSMC

TSMC는 새 노광장비 2대를 들여오는 것과 별도로 기존에 운영하던 2대의 성능을 향상시키는 업그레이드 작업에 착수하기로 했다.

이들 장비는 내년부터 양산에 들어가는 16나노 공정 반도체 생산에 투입될 전망이다. 최고 7나노 공정까지 활용될 것으로 보인다.

ASML측은 노광장비 한 대가 당장은 하루에 웨이퍼 500장 가량을 처리할 수 있을 것으로 보고 있다. 하지만 내년 양산 시기쯤이면 하루 1500장까지 올라갈 것으로 내다 봤다.

ASML의 영향력은 반도체 제조회사들에겐 그야말로 절대적이다. 작은 면적에 더 많은 반도체 회로를 그려 넣기 위해 미세공정의 한계를 끊임없이 뛰어넘어야 한다. 이런 이유로 반도체 업계 종사자들 사이에서는 “ASML의 진보 없이는 삼성과 인텔의 진보도 없다”라는 말까지 나온다. 삼성전자와 인텔,TSMC가 2012년 앞다퉈 ASML의 지분을 매입하고, 3 사가 힘을 합쳐 7조원을 투자한 것도 이런 속내가 작용했다.

반도체 업계에는 마이크로칩의 저장용량이 18개월마다 2배로 커진다는 ‘무어의 법칙(Moore’s law)’이 있는데 있다. 회로 선폭(線幅)이 좁을수록 같은 면적에 더 많은 회로를 집어넣을 수 있어 저장 용량이 커지고, 성능이 개선된다는 것이다.

실제로 20나노 공정은 기존 25나노보다 데이터전송 속도가 30% 정도 더 빠르고, 작동에 필요한 전압이 20% 가량 낮다. 하지만 이 법칙은 20나노 미만에서는 통하지 않는다. 더 미세한 회로를 노광기가 그리지 못한다. 반도체 제조사들은 회로 밑그림을 여러 번 덧칠하는 ‘더블패터닝’, ‘쿼드러플 패터닝’ 등 다양한 보완책을 찾아왔다.

이런 가운데 ASML이 이번에 출시한 장비는 반도체 회로도를 그리는 빛의 속도와 정확도를 높였다. 그동안 한계에 다다랐던 ‘무어의 법칙’을 당분간 이어준 기술이란 평가까지 나온다.

복잡한 패터닝 기술을 사용할 필요가 없어 양산 효율도 뛰어날 것이란 전망도 나온다.

◆ 바빠진 삼성·인텔

삼성전자와 인텔은 아직까지 새 노광장비를 구매했다는 발표를 내놓지 않고 있다. 그동안 ASML이 지분 순서대로 차세대 장비를 공급했던 점을 감안하면 지분 18%로 가장 많은 인텔이 가장 먼저이고, 5%를 가진 TSMC, 3%를 보유한 삼성전자 순으로 장비를 공급받게 될 것으로 보인다.

인텔은 7나노 공정 양산 준비에 돌입했지만 충분한 수준의 극자외선 노광기술을 확보하지는 못한 것으로 알려졌다. ASML은 인텔이 이런 이유로 양산 효율을 높이는 쿼드러플 패터닝 기술을 우선 활용하고 2018년쯤에야 새 장비를 투입할 것으로 전망했다.

삼성전자도 인텔과 처지가 크게 다르지 않은 것으로 보인다. 당장 14나노 핀펫 양산 수율을 확보해야 하기 때문이다. 삼성전자는 시스템반도체 미세공정인 14nm(나노미터) ‘핀펫 기술’을 앞세워 파운드리(수탁생산) 반도체 사업 경쟁력을 강화할 계획이다.